IPM-NVMe2NVMe

NVMe to NVMe Reference Design

Add your own magic potion on data management

Overview

This architecture proposal is based on NVMe offloaded IPs. It is integrated in a FPGA and could be also be integrated in ASIC, allowing to provide design flexibility and the ability to add processing accelerator IPs, computational storage…. IPM-NVME2NVMe solution is the perfect base to add easily your own custom logic such as erasure coding and duplication, RAID system, encryption, compression…

- NVM Express Compliant

- 1 to X host interfaces

- Add your own custom logic like encryption, compression, your own magic potion!

Related IP cores

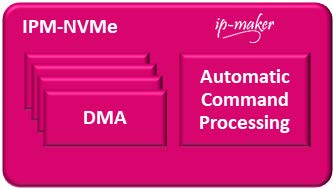

IPM-NVMe_Device IP core

The IPM-NVMe_Device IP core is a verilog IP ready to be integrated in a FPGA/ASIC. IP-Maker has developed a full hardware implementation of the NVMe protocol on the device side. It is based on an Automatic Command Processing Unit and a multi-channel DMA to perform data transfers.

This architecture is easy to integrate with standard interfaces (AXI/Avalon), between the PCIe and memory controllers. This low latency design is ready to support emerging memories, such as MRAM and ReRAM technologies. The IP-Maker IP-NVMe_Device IP is UNH-IOL NVM Express compliant.

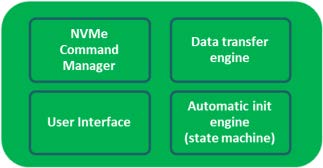

IPM-NVMe_Host IP Core

The IPM-NVMe_Host IP core is a verilog IP ready to be integrated in a FPGA/ASIC. This IP is a full hardware implementation of the NVMe protocol on the host side. It manages the NVMe commands and the data transfer without requiring any software (included system initialization) and without any specific knowledge.

This offload engine avoids the use of CPUs, delivering a best-in-class performance/power NVMe host controller. It can be used with any compliant PCIe NVMe SSD available on the market.

INVMe2NVMe_firmware

IP-Maker provides a basic data flow management software. It is an excellent starting point to design your own specific NVMe-to-NVMe HBA.