IPM-NVMe_Host

High Performance Embedded Host NVMe

Overview

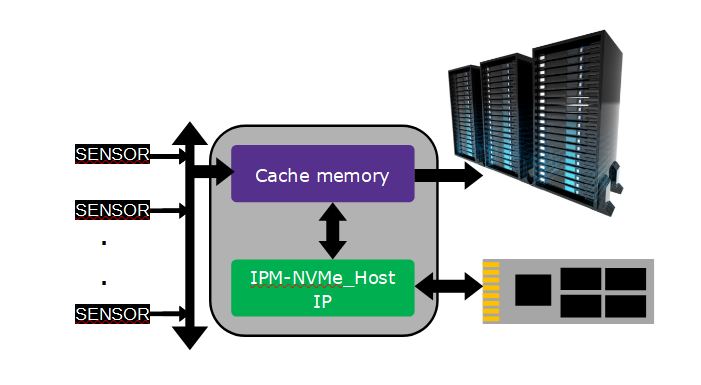

The IPM-NVMe_Host core is a verilog IP to be integrated in a FPGA or ASIC design. It fully manages the NVMe and PCIe protocol on the host side without requiring any CPU and any specific knowledge. It can be used with any NVMe SSD available on the market, or with a custom design based on the IPM-NVMe_Device IP from IP-Maker.

The IPM-NVMe_Host is well suited for embedded applications requiring a high throughput storage such as recorder and video applications. 1+ million IOPS performance requires the use of an expensive CPU, which is not feasible in an embedded system due to cost, space and power limitation.

- Automatic PCIe/NVMe initialization

- RAM or AXI4 or Avalon interface

- Scalable architecture

- options:

- Opal 2.0 management

- multiple queues management

- Ultra low latency

- Very high throughput

- No need of CPU

- Ease of useNo specific knowledge required

Using the pre-validated IPM-NVMe_Host IP core greatly reduces time-to-market for storage OEM; this allows the OEM to benefit from a powerful data transfer manager. The IPM-NVMe_Host IP core is full featured and easy to use with multiple application interface such as AXI or RAM-like.

As the first NVMe IP core supplier, IP-Maker’s experience regarding NVMe’s development is unmatched. Moreover, it provides the IPM-NVMe_Device controller for data storage applications, such as NVMe SSD and NVMe NVRAM.

Description

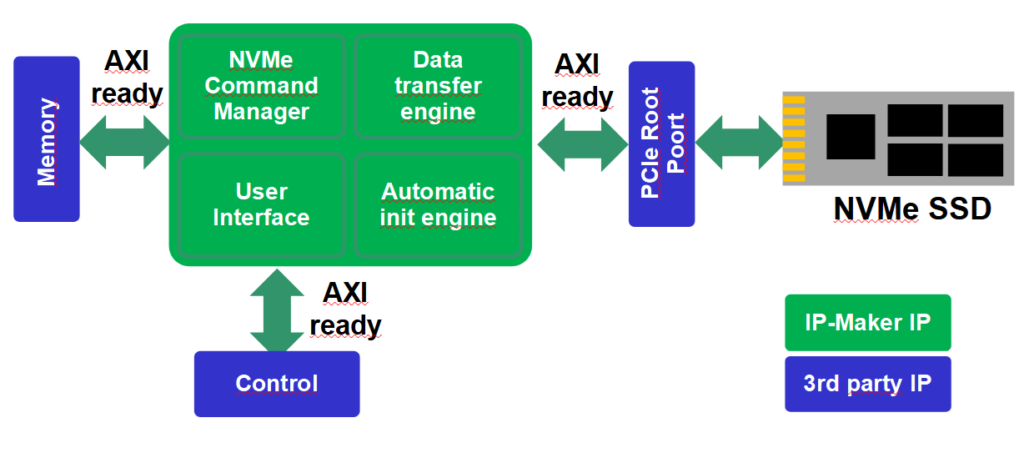

- Automatic init engine: PCIe and NVMe device initialization, hardware discovering

- User Interface: memory configuration and input for the transfer request by the API

- NVMe command manager: translation of the data request from API into a NVMe command. Submission and completion pointers management

- Data Transfer Engine: management of the data transfer between the NVMe SSD and the FIFO/memory

Reference design

Board ready for evaluation are

- Xilinx KCU105

- Xilinx ZCU106

- Xilinx VMK 180

- Fidus Sidewinder

- Altera Aria 10